Come aveva già accennato Alessio Di Domizio nell’articolo sull’Amiga 3000 , alcuni dettagli tecnici di questo computer meritavano una trattazione a parte che tenesse anche conto della sua evoluzione che, purtroppo, non vide mai la luce a causa delle “brillanti” menti a cui erano affidate le redini dell’azienda.

L’Amiga 3000+ si colloca sicuramente nel mito per quanto riguarda le leggende che lo circondano ma, a differenza delle fantasie popolari, c’è ben più di un fondo di verità che gli appartiene, in quanto alcuni modelli hanno visto la luce, e uno di essi è nelle mani del suo principale progettista, un altro mito della casa: Dave Haynie.

Cominciamo col dire che, come accennato e come si poteva già intuire dal nome, questo progetto fonda le sue radici sul modello 3000, partendo dal case fino ad arrivare alla CPU, alla memoria, e in generale alla dotazione di periferiche che accompagnavano quello che possiamo definire come il miglior prodotto che Commodore abbia commercializzato.

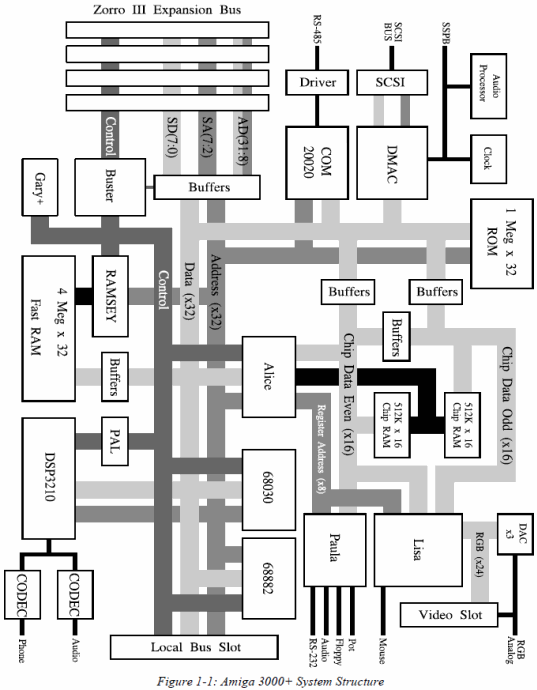

Rispetto al suo predecessore i miglioramenti riguardano le seguenti macroaree:

- nuovo chipset AGA

- DSP AT&T 3210

- nuovi dispositivi di I/O

- layout della memoria razionalizzato

Per quanto riguarda l’AGA, maggiori informazioni si possono trovare nell’apposito articolo che lo riguarda, a cui va necessariamente affiancato quello sull’ECS , per comprendere meglio le differenze esistenti fra l’Amiga 3000 (che montava proprio l’ECS) e il 3000+.

Sebbene l’AGA abbia rappresentato una notevole (e attesa) ventata di novità (fra le quali è d’obbligo ricordare l’introduzione della palette da 16 milioni di colori, modalità video disponibili per diverse risoluzioni, 8 bitplane, e sprite larghi fino a 64 pixel), la punta di diamante rimane il DSP 3210 di casa AT&T, che mette in ombra l’accoppiata 68030 e 68882 a 25Mhz, che pure sono gli elementi principali dell’intero sistema.

Grazie a un clock di 50Mhz questo dispositivo è in grado di erogare 12,5 MIPS e 25 MFLOPS. Se il primo dato non è particolarmente impressionante (il 68030 a 25Mhz arrivava a poco più di 8 MIPS), il secondo lo è sicuramente, tenendo in debito conto i numeri che giravano all’epoca. L’appena presentato 68040, considerato un autentico mostro macina-numeri, si doveva accontentare di “soli” 3,5 MFLOPS a 25Mhz…

Senza andare troppo nei dettagli sul funzionamento di questo chip, i motivi del suo inserimento sono da ricercarsi nella sperimentazione di nuove idee su come poter migliorare le prestazioni del sistema cercando di scaricare a dispositivi dedicati alcuni compiti a loro particolarmente affini.

Dopo Copper e Blitter si fa strada, quindi, un nuovo coprocessore particolarmente versato per l’elaborazione di segnali (d’altra parte il nome appare eloquente: Digital Signal Processor), ma utilizzabile anche per diversi altri scopi, grazie all’intrinseca programmabilità.

La versatilità che lo contraddistingue permette di impiegarlo tanto nel campionamento e manipolazione di segnale audio a 16 bit e 44Khz (qualità CD, per intenderci), quanto nell’implementazione dei protocolli di comunicazioni su cui si basano i modem e i fax. Per questi ultimi il limite del chip è rappresentato dallo standard V32-ter, che arriva fino a 19200 bit al secondo.

Ovviamente l’uso per cui era stato maggiormente pensato era quello del campionamento e della riproduzione di segnali audio a 16 bit e 44Khz, da troppo tempo attesi dagli affezionati amighisti, che vedevano arrancare in parte i loro computer a causa delle evoluzioni della famigerata SoundBlaster per PC (ma non dimentichiamo anche la GUS arrivata poco dopo).

Per poter gestire entrambi i casi, al DSP sono collegati due opportuni codec, che integrano anche i due convertitori A/D e D/A, i quali si occupano rispettivamente di campionare e riprodurre i segnali con cui hanno a che fare. In particolare il codec audio è in grado di arrivare a frequenze di 48 Khz, e supporta una discreta varietà di formati per i campioni (8/16 bit, 8-bit μ/A-low).

Non sarebbe, quindi, utilizzabile per soppiantare completamente la CPU (e diventare tale), ma rimane una periferica con un elevato margine di indipendenza e flessibilità, essendo anche in grado di interrompere il 68030 (potendo generare due interrupt, di livello 2 e 6) e a sua volta d’essere interrotto da esso (con altri due interrupt utilizzabili).

Inoltre dispone di un canale DMA per l’accesso alla memoria o a periferiche, di un timer programmabile (per generare interrupt interni), e infine di un bus seriale per comunicare con fino a 4 veloci porte seriali, che nello specifico sono collegate ai codec di cui sopra e con un’espansione che gli avrebbe consentito di interagire con eventuali altri DSP 3210.

Già, perché su questo processore gira un apposito “sistema operativo” (in realtà dovremmo chiamarla applicazione di controllo, in quanto il DSP non è una CPU vera e propria) sviluppato da AT&T, chiamato VCOS, che è in grado gestire e schedulare più processi da smistare ai vari DSP disponibili nel sistema, che diventa quindi massicciamente parallelo (se sfruttato opportunamente).

Oltre alla linea per il telefono, agli ingressi e alle uscite audio a 16 bit, e al connettore d’espansione per il DSP, il 3000+ mette a disposizione altri dispositivi di I/O, nuovi o migliorati. Al “local bus” (connettore di espansione per la CPU) sono stati aggiunti nuovi segnali, e il video slot presenta adesso una completa gamma di segnali per il video, l’audio, e il genlock.

Gli slot di espansione Zorro III supportano tutte le caratteristiche di questo bus; è presente anche un connettore CD/Aux per collegare un lettore CD al computer, e infine una speciale porta seriale simile all’I²C ideata da Philips (e a cui possono anche interfacciarsi periferiche che implementano questo protocollo) per collegare altri dispositivi (a bassa velocità).

Molto più interessante è la presenza di una porta di rete, che in precedenza si trovava solamente nei modelli di Amiga 3000 realizzati per far girare Unix come s.o., in quanto permette di collegare il 3000+ ad altre macchine realizzando network a basso costo che arrivano fino a 2,5Mb/s di banda.

Altri miglioramenti li ritroviamo nel chip di gestione della memoria di sistema (Ramsey, che adesso è in grado di controllare fino a 16MB in diverse modalità), e nel controller DMA (DMAC, con un buffer FIFO più capiente, e adesso in grado di gestire anche accessi a 16 bit anziché soltanto a 32 bit) a cui è collegato il controller SCSI che si occupa di comunicare con periferiche esterne che supportano questo protocollo.

Per quest’ultimo è bene spendere qualche parola in più per sottolineare la bontà della scelta che Commodore (anzi, i suoi ingegneri) aveva fatto con l’Amiga 3000, dotando questo computer di una porta SCSI che gli consentiva non soltanto di poter accedere a un vasto ed eterogeneo (non soltanto hard disk e lettori CD) parco di dispositivi, ma di farlo in maniera estremamente veloce e scaricando quasi del tutto la CPU dalla loro gestione.

Non a caso ancora oggi gli hard disk SCSI rappresentano la scelta primaria per server in cui l’I/O sia un fattore molto importante (quantunque le ultime evoluzioni dell’ATA offrano un ottimo rapporto prezzo / prestazioni). Vedremo come con l’Amiga 4000 Commodore deciderà di ripiegare sulla più economica, ben più scarsa, e inefficiente interfaccia EIDE…

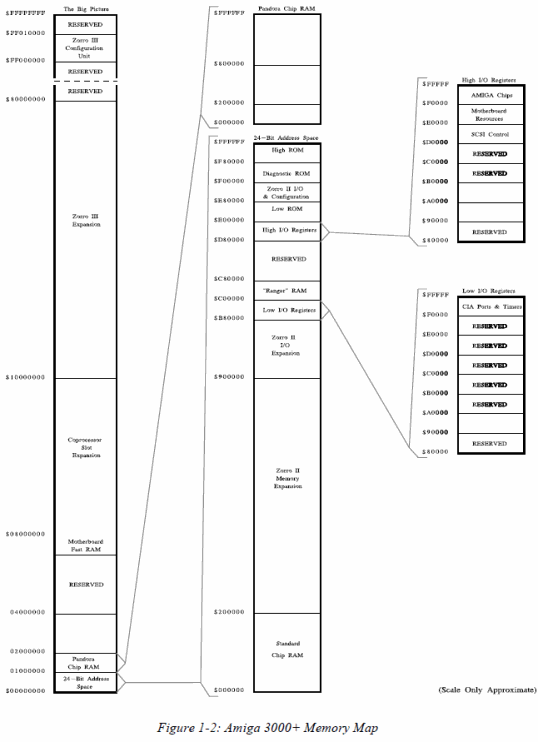

Per quanto riguarda il layout della memoria, sono da segnalare alcune interessanti informazioni che ci permettono di comprendere la lungimiranza dei progettisti di questo gioiello tecnologico. L’Amiga ha dovuto fare i conti con l’originario spazio d’indirizzamento a 24 bit, in cui sono state dislocate diverse aree di memoria (chip ram, fast ram a 16 bit, ROM, chip custom, chip di I/O, e configurazione delle periferiche su bus Zorro):

Questo ha comportato la definizione di precisi limiti per ogni area, che ne hanno in un certo qual senso soffocato e vincolato lo sviluppo (o estensione che dir si voglia). Se per la RAM questo non ha rappresentato più di tanto un problema, in quanto i processori dotati di bus indirizzi a 32 bit, e i relativi slot Zorro III che li sfruttavano (come pure la memoria integrata), erano in grado di mappare la memoria “fast” a 32 bit oltre il limite dei 16MB dei 24 bit “bassi”, lo era per tutto il resto.

In particolare la ROM era vincolata a 512KB di spazio contiguo, a cui si sommavano altri 512KB mappati a un altro indirizzo e utilizzabili allo scopo, per un totale di 1MB quindi. Ma la situazione ben più grave era rappresentata dalla chip ram, col suo intrinseco limite di 2MB della memoria bassa, che con l’introduzione del chipset AGA si faceva sempre più pesante.

La soluzione trovata dagli ingegneri è stata quella di utilizzare degli alias per entrambi i tipi di memoria. La ROM è stata portata, infatti, a un totale di 4MB, ma con due banchi da 512KB mappati agli indirizzi “tradizionali” ($00F80000 per la parte alta, e $00E80000 per la parte bassa). In questo modo il vecchio codice continua a funzionare regolarmente, mentre il nuovo gira nella memoria alta (non ci sono indicazioni, ma presumibilmente negli ultimi 4MB dei 4GB teoricamente indirizzabili).

Soluzione simile per la chip ram, il cui limite è stato innalzato a ben 16MB, con questa memoria mappata tutta all’indirizzo $01000000, mentre i primi 2MB continuano a essere mappati al canonico indirizzo $00000000. In questo modo le vecchie applicazioni potevano girare tranquillamente perché trovavano la memoria esattamente dov’è sempre stata, mentre quelle nuove potevano accedere al maggior quantitativo eventualmente a disposizione sfruttando il nuovo spazio d’indirizzamento.

Non sorprende, a questo punto, leggere dal documento di descrizione dell’Amiga 3000+ che il chipset AGA era in grado di supportare direttamente fino all’incredibile quantità 8MB di chip ram: chissà cosa si sarebbe potuto fare!

E non sorprende neppure sapere che, nonostante fosse sostanzialmente finalizzato (ci sono state ben 3 revisioni), il progetto Amiga 3000+ fu abbandonato dalla Commodore perché ritenuto troppo costoso, per ripiegare sul ben più economico (quindi più redditizio), ma anche … castrato Amiga 4000.

Tutto ciò a testimonianza dell’enorme diversità di vedute fra il team dei progettisti, che continuavano a “pensare in grande” (e alle innovazioni) e a quei “genii” del marketing che avevano fisso in testa il chiodo dei bigliettoni verdi senza cuore né passione, che hanno poi portato al fallimento di questa gloriosa casa.