In passato il buon Alessio Di Domizio mi aveva suggerito di scrivere qualcosa sull’appena annunciato AmigaOne X1000 di A-Eon, un “Amiga” di nuova generazione basato su una CPU PowerPC, di cui però all’epoca si sapeva poco. Di recente è stata ufficializzata l’adozione della CPU, una PA6T-1682M a 1,8Ghz prodotta da PA-Semi, e nel frattempo era stata annunciata anche una nuova scheda madre all-in-one (a cui manca solo la RAM) della linea Sam di ACube.

Tutto ciò, assieme ad altri fatti che tratterò, mi ha indotto a scrivere alcuni articoli sul tema, esaminando queste novità (che sarebbero dovute arrivate a fine dello scorso anno, ma per diversi motivi sono state posticipate al nuovo) che andranno a rinverdire un mercato rimasto un po’ stagnante, alla luce anche della storia passata (in particolare riguardo alle CPU) e delle prospettive future.

Intanto preciso che ho virgolettato la parola Amiga (di seguito la ometterò per comodità) perché, come ho ripetuto diverse volte, ha da sempre rappresentato un connubio fra hardware custom (unico) e software, che personalmente non ho ritrovato nelle macchine che hanno continuato a utilizzare quest’etichetta, basate su componentistica a disposizione sul mercato.

Si tratta di una convinzione che non chiedo a nessuno di sposare, ma consentitemi almeno di poterla esprimerla in modo che sia quanto meno chiaro il mio pensiero in merito. Alle meravigliose macchine di casa Commodore è, pertanto, sopravvissuto il solo sistema operativo, AmigaOS, incarnato poi in “successori” più o meno legittimi: AROS (il più vecchio e non “ufficiale”, ma multipiattaforma), MorphOS (“non ufficiale”) e AmigaOS 4 (“ufficiale”: basato sui sorgenti originali).

Senza andare a rinvangarne la storia nel dettaglio, con la decisione di Motorola di abbandonare la sua fortunata (e ancora rimpianta) linea di microprocessori 68K (di cui il 68060 è stato l’ultimo rappresentante) abbracciando Apple e IBM nell’avventura PowerPC, cominciarono a fiorire schede acceleratrici per gli Amiga esistenti basati su questi nuovi processori, che costituirono il trampolino di lancio per patch ad AmigaOS (per usarli come coprocessori), porting di alcune parti, fino a s.o. completi (fra cui i citati) in grado di sfruttarli.

Da lì in poi le nuove macchine Amiga sono divenute sinonimo di computer equipaggiati con processori di questa famiglia, per cui è evidente che le aspettative degli utenti rimasti legati a questa piattaforma (o filosofia?) hanno puntato l’attenzione sull’evoluzione della sua architettura, nelle varie incarnazioni fornite da IBM e Motorola (divenuta poi FreeScale), fino ad arrivare ad altri licenziatari (come Applied Micro, fornitore dei modelli impiegati nelle schede SAM).

Finché Apple è rimasta legata a queste CPU per le sue macchine, i miglioramenti si sono visti e dei PowerPC sono stati forniti diversi modelli oltre che rinnovamenti architetturali (dalla linea 600 alla 700, poi al G4 , al G4+, e infine al PPC970 aka G5), alcuni dei quali utilizzati anche in sistemi Amiga (AmigaOne, Pegasos ed EFIKA).

Col passaggio di Apple agli “odiati” x86 di Intel (ma poi, “inspiegabilmente”, amatissimi; misteri della “fede”), lo sviluppo dei PowerPC ha subìto una brusca frenata, costringendo IBM ad abbandonare il segmento desktop (continuando soltanto in quelli in cui ha sempre operato: server coi POWER, e PowerPC per le soluzioni customizzate per le console), e FreeScale a convertire anche la linea G4 al settore embedded/SoC (l’ultimo rappresentante, il 7448, è, infatti, alla base della nuova famiglia e600 creata allo scopo).

Di riflesso chi ha operato nel settore Amiga ha dovuto necessariamente ripiegare sull’esistente o, come vedremo, andando a pescare soltanto da soluzioni embedded, con tutti i limiti (ma anche vantaggi) che una scelta simile può avere. E’ così che AmigaOne per il nuovo X1000 ha optato per il PA6T-1682M di PA-Semi, SoC dual core pensato per sistemi embedded e applicazioni militari a basso consumo, ma che presenta buone caratteristiche che lo rendono papabile anche per un utilizzo desktop.

Si tratta di una nuova architettura PowerPC, che non trova similitudini con le altre, ma che grosso modo mi sento di allineare al PowerPC 970/G5 di IBM, in quanto è pensata per operare a elevate frequenze (grazie a una lunga pipeline id 14 stadi “base”; 16 per il G5), la presenza dell’estensione SIMD Altivec, la possibilità di poter estrarre un buon numero di istruzioni per ciclo di clock (fino a 3), la capacità (o necessità) di suddividere le istruzioni più complesse in micro-op (istruzioni più semplici), e di mantenerne “in volo” (in attesa di esecuzione) un buon numero (fino a 64).

Preciso che il G5 punta, comunque, a ottenere prestazioni più elevate, essendo stato progettato allo scopo (in realtà, derivando dal POWER4, ne ha “ereditato” questa caratteristica). Consente, infatti, di estrarre fino a 5 istruzioni per ciclo di clock (di cui una può essere solamente un salto), mantenerne 200 da eseguire, ed è dotato di numerose unità di esecuzione per poterle “sfamare”.

Molto positiva la presenza di 64KB di cache L1 per il codice e altrettanti per i dati, a cui si affiancano 2MB di cache L2, mentre il G5 ha soltanto 32KB di cache per i dati e 512KB di cache L2 (per il primo modello; l’ultimo, il 970MP, ne ha 1MB per singolo core), ma in ogni caso le cache presentano caratteristiche diverse (il fatto di essere unica e separata ne è già un esempio), come diversi sono i bus per interfacciarsi con la memoria e le periferiche (il PA6T-1682M ha 2 controller DDR2, e un bus per l’I/O, mentre il G5 ha un solo bus, simmetrico, per interfacciarsi col chipset, e da questo alla memoria), e idem per l’unità di branch prediction (giusto per sottolineare le distanze, il primo ha una branch history da 32K entry, mentre il secondo ne ha 3 da 16K).

Le differenze, quindi, ci sono (d’altra parte i due progetti sono radicalmente diversi), per cui dal punto di vista prestazionale confronti precisi è difficile farne; tutto dipenderà dal tipo di codice che andranno a eseguire, e quindi bisognerà vedere “sul campo” come si comporterà questo nuovo arrivato, anche se la mia impressione è che gli ultimi G5 dovrebbero risultare leggermente superiori.

Per chi ha bisogno di numeri per eventuali “misure”, al momento gli unici dati disponibili sono quelli della nota suite di benchmark SPEC, che accreditano di 1100 SPECint 2000 e 2255 SPECFP 2000 il PA6T-1682M a 2Ghz (e dual core), 937 e 1051 per il primo G5 a 1,8GHz (e singolo core), mentre per il PPC970MP a 2,5Ghz (e dual core) 1438 e 2076. Dati che, lo sottolineo, vanno presi con le pinze, soprattutto considerando che si tratta di benchmark (io preferisco sempre delle applicazioni reali in questi casi).

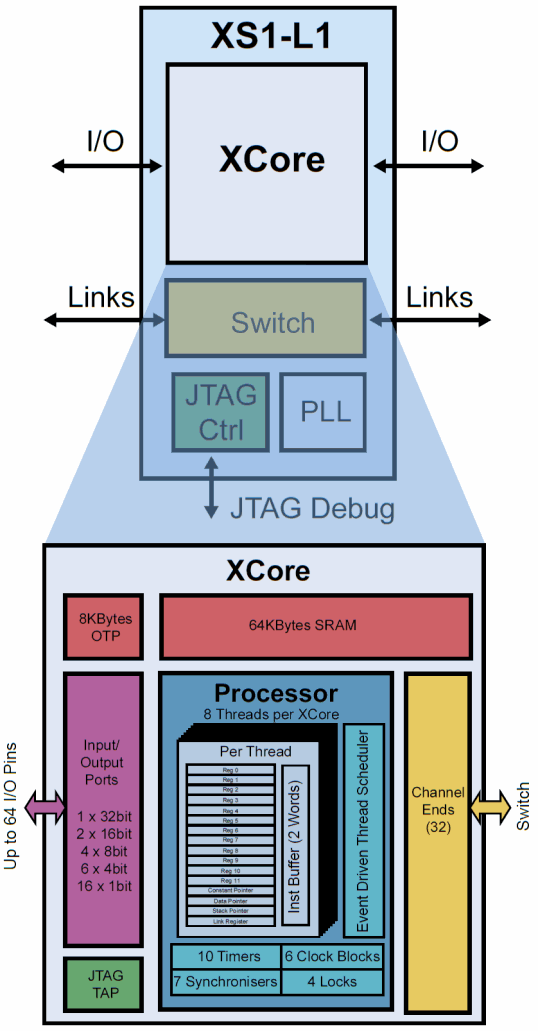

Molto si è detto e speculato (soprattutto favoleggiato) anche sul coprocessore che affiancherà la CPU, denominato Xena, e anch’esso prelevato direttamente dal settore embedded. Si tratta di un componente pensato esclusivamente per gestire e manipolare l’I/O sfruttando un core in grado di eseguire fino a 8 thread (tramite uno scheduler che determina quale dev’essere eseguito in quel momento) che possono anche essere attivati in base al verificarsi di eventi esterni o interni (nel chip sono presenti anche 10 timer).

Infatti questo processore non ha un bus collegato alla memoria, ma una serie di pin (chiamati link) configurabili a piacimento in ingresso, uscita, o bidirezionalmente, e che possono eventualmente attivare un particolare thread per rispondere immediatamente a un evento esterno. Potenzialmente è anche in grado di accedere a memorie esterne, a seconda di come viene programmato (l’utilizzo che se ne fa dei pin è del tutto arbitrario).

La sua forza è, quindi, rappresentata dalla connettività, e a tal fine è possibile collegarlo con eventuali altri chip della stessa famiglia (fino a 8) tramite pin settati appositamente per fungere da canali di comunicazione. Qualcosa che ricorda molto i leggendari Transputer di Inmos, per chi ha avuto modo di conoscerli o sentirne parlare. Ovviamente anche i thread possono comunicare internamente fra di loro sfruttando degli appositi canali.

Il bus Xorro di questa macchina, derivato dal PCI-Express, nasce proprio per mettere a disposizione diversi pin collegati poi direttamente a Xena, così da poter essere utilizzati per gli usi più disparati, fra i quali, come già detto, la comunicazione con eventuali altri processori dello stesso tipo (in ottica di espansione della potenza di calcolo e/o flessibilità del sistema).

Dovrebbe esser chiara la sua vocazione a questo punto, e infatti che non c’è da aspettarsi potenza bruta, tant’è che il chip a 500Mhz è in grado di arrivare a 500MIPS. Se consideriamo che uno solo dei due core della CPU sulla carta è capace di erogare 3600MIPS, si capisce bene a chi ci si deve rivolgere per i calcoli massicci, fermo restando che i processori non si confrontano sulla base dei MIPS (i dati li ho forniti soltanto per dare un’idea).

D’altra parte anche lo schema di funzionamento interno del chip porta a capire in che modo lavora e, pertanto, come si dovrà programmarlo:

8KB di memoria servono per il bootstrap del chip, mentre i thread per lavorare hanno a disposizione 64KB di SRAM in totale, oltre ovviamente a diverse altre risorse, gli immancabili link per l’I/O, e i canali di comunicazione.

Il core è rappresentato da un RISC a 32 bit dotato di istruzioni a 16 bit per le operazioni più comuni, e a 32 bit per quelle più rare, in modo da ottenere una maggior densità di codice; l’architettura interna è semplice, costituita da 12 registri general purpose e 5 speciali / dedicati, ma è dotata anche di numerose istruzioni per svariati compiti (fra cui la gestione di canali ed eventi, come c’era da aspettarsi).

Chi pensava di caricare compiti a raffica su questo gioiellino per scaricare, a sua volta, la CPU è avvisato: programmarlo non è affatto semplice, e richiede un certo ingegno per sfruttare al meglio le risorse che mette a disposizione (64KB di memoria sono veramente pochi).

Sempre in tema di sfruttamento di questo nuovo componente, in quanto nuovo porta con sé anche nuove problematiche. Ad esempio, la sua gestione sarà totalmente a carico del s.o. o delle applicazioni? Verranno esposte delle apposite API e/o un device?

Le risposte a queste domande aprono scenari diversi, ma una cosa (ovvia) si può dire sicuramente: ci sarà bisogno di apposito codice, e quindi sviluppatori che lo dovranno scrivere. Con la penuria di gente che attanaglia la comunità AmigaOS, inclusi gli stessi produttori dei s.o., arriverà mai il supporto? Sarà adeguato? Quando arriverà? Il rischio concreto e reale è che questo aggeggio rimarrà un bel “soprammobile”, anche a motivo delle sue particolarissime caratteristiche.

Il resto della dotazione è abbastanza standard, e include: scheda grafica basata sulla famiglia R700 di AMD (serie Radeon HD 4×00, ma sul modello preciso non ci sono ancora notizie), audio 7.1, memoria DDR2 (la CPU la supporta fino a 1066Mhz, ma il dato finale non è noto), PCI-Express (anche 16x), PCI, SATA-2, IDE, USB2, Gigabit Ethernet, ecc., e l’immancabile annesso case con la classica boing ball in rilievo.

Anche il prezzo non è ancora noto, ma sembra che alcune schede madri dotate di memoria (quindi senza case, disco rigido, ecc.) siano state vendute, a prezzo agevolato, per circa 1600€ ad alcuni sviluppatori. Se queste indiscrezioni dovessero rivelarsi vere, l’utente finale dovrà sborsare più di 2000€ per accaparrarsene uno, cifra questa decisamente elevata che metterà un freno alle ambizioni di molti appassionati.

Ci sarebbero ancora alcune considerazioni da fare sulla scheda video, ma preferisco rimandarle all’articolo di chiusura del tema Amiga PowerPC, che seguirà quello dedicato alla nuova Sam460ex (con un occhio anche al primo modello, la Sam440ep, più che altro per effettuare qualche confronto), perché le riflessioni hanno una portata più generale sul panorama AmigaOS e hardware annesso.