Continuiamo la rubrica settimanale dedicata al mondo del raffreddamento, per brevità battezzata The Hot Spot, con un articolo concernente una delle innovazioni che rivoluzioneranno il mondo dei semiconduttori, e le relative metodologie di raffreddamento.

L’industria dei semiconduttori ha raggiunto nel tempo uno stadio in cui le tecnologie oggi disponibili ci permettono di assistere a continui e frequenti stravolgimenti nel design, nell’implementazione e nella scalabilità dei computer, così come nel modo di utilizzarli. Anche se la Legge di Moore ha anticipato e caratterizzato l’evoluzione dei sistemi di calcolo nelle ultime decadi, essa stessa si trova a fronteggiare attualmente enormi limitazioni, superabili solo attraverso un diverso approccio nella produzione di chip, consistente in pratica nella sovrapposizione di diversi strati, o stack: un chip tridimensionale in grado di garantire così l’integrazione di diversi componenti, l’uno sull’altro, nello spazio ridotto di un chip tradizionale a due dimensioni.

Se da un lato questa nuova tecnologia “3D” apre incredibili possibilità e potenzialità, dall’altra ci pone di fronte a problematiche progettuali non indifferenti, tra cui quello della gestione del calore prodotto da simili soluzioni, non meno importante dei metodi di produzione veri e propri dei chip tridimensionali.

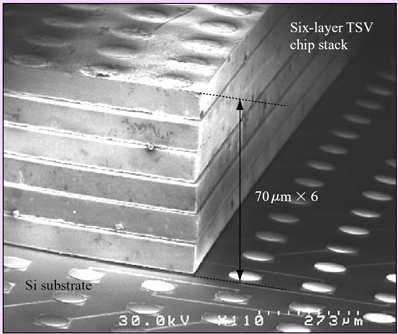

L’immagine sottostante mostra uno stack di sei chip, ciascuno spesso solo 70 micromètri (µm) sovrapposti l’uno sull’altro e posizionati sopra un substrato di silicio, che funge da base:

All’inizio del 2007 l’IBM annunciava di aver terminato la fase di design e ricerca, durata una decina di anni, avente appunto come obiettivo la produzione in larga scala di chip multistrato, la cui caratteristica principale era appunto essere costituito da una serie di strati sovrapposti di chip sottili (Thin Chip) interconnessi tra di loro, così da diminuire drasticamente la lunghezza delle piste di interconnessione, rendendo a tutti gli effetti obsoleta la legge di Moore, una volta per tutte.

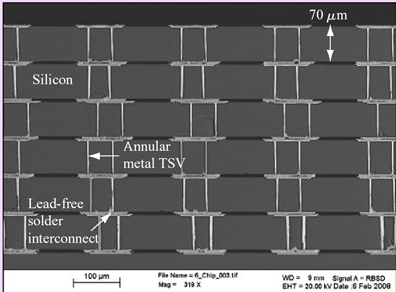

Per consentire l’interconnessione tra i vari strati di componenti, che a tutti gli effetti possono essere considerati chip 2D essi stessi, l’IBM ha adottato una tecnologia denominata TSV (Through-Silicon Vias) che in pratica consiste in sottili forature di diverse forme che vengono ricavate direttamente nei singoli wafer di silicio, e che una volta sovrapposti vengono riempiti con leghe di metallo in assenza di piombo, attraverso una tecnica di riflusso, permettendo il consolidarsi del contatto elettrico tra i vari strati di chip.

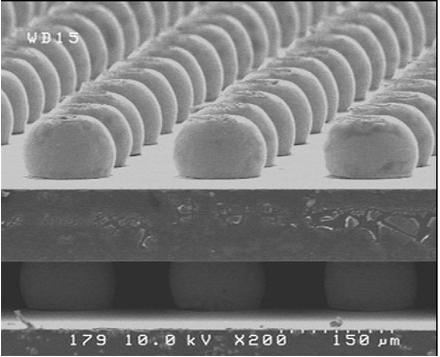

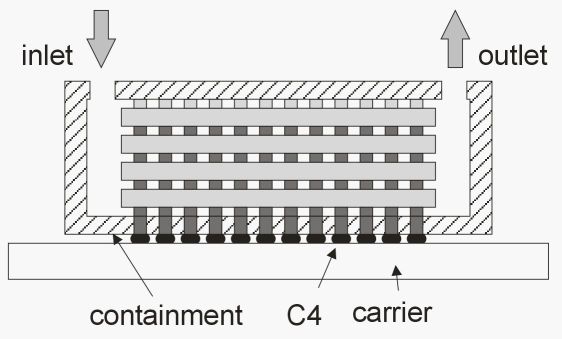

Per impedire che si generino corto circuiti tra i vari chip, gli strati vengono separati da microsfere di materiale ferroso, una tecnica denominata C4 (controlled-collapse chip connection). Il risultato è uno stack di sottili chip 2D sovrapposti, interconnessi, estremamente resistente alle sollecitazioni meccaniche e termiche, che si sviluppa in verticale e non più in orizzontale.

Tralasciando le molteplici difficoltà di realizzazione di una struttura a stack di chip, come per esempio l’integrità delle interconnessioni e la loro solidità (sia in termini di resistenza fisica che termica), gli sviluppatori si sono dovuti soprattutto scontrare con un problema che affligge tutti i chip 2D, e in questo caso aumentato in misura esponenziale data la struttura multistrato del chip 3D: la dissipazione del calore prodotto durante il funzionamento.

Nei chip tradizionali la dissipazione del calore infatti avviene tramite l’apposizione di un dissipatore di calore di metallo (alluminio o rame) che a sua volta viene raffreddato da un fluido (aria o acqua). Nei chip 3D questa soluzione ha enormi limiti, in quanto l’apposizione di un dissipatore sullo strato inferiore di silicio del chip rimuoverebbe efficacemente solo il calore dello strato direttamente a contatto con esso, non raffreddando efficacemente gli altri strati.

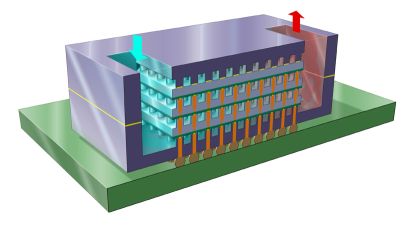

Per risolvere questo problema, il Fraunhofer Institute di Berlino, che collabora con il centro ricerche di IBM, ha sviluppato ad inizio del 2008 una tecnologia di raffreddamento con liquido (acqua) capace di rimuovere efficacemente il calore prodotto da tutti gli strati del chip 3D, contemporaneamente. Il sistema consiste in micro-canalizzazioni che, sfruttando lo spazio tra i vari strati di chip creatisi tramite le interconnesioni dei singoli stack con la tecnologia C4 e debitamente isolati, permette il passaggio di acqua asportando il calore direttamente dalla fonte.

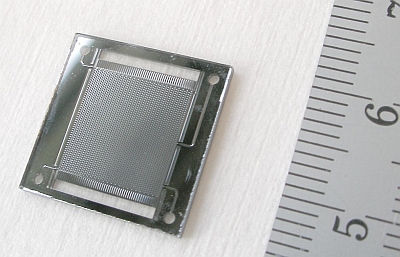

Per evitare cortocircuiti il sistema di produzione prevede che le zone di interconnessione vengano sigillate da un sottile strato di silicio, o thin layer, evitando che il liquido causi problemi anche di corrosione. Una volta che lo stack di chip è pronto, questo viene posizionato all’interno di un contenitore di silicio, che servirà allo scopo di contenere lo stack e di evitare fuoriuscite di liquido. Una volta sigillato, verrà pompato liquido al suo interno che attraverserà i vari strati di chip, e ne uscirà asportando il calore prodotto dal chip. Secondo simulazioni effettuate, tale sistema di raffreddamento dovrebbe essere capace di smaltire fino a 180W per centimetro quadrato.

La tecnologia di chip stacking permetterebbe dunque di impilare chip uguali l’uno sull’altro, così da formare microscopici cluster computazionali, a beneficio della velocità di calcolo, ma anche di sovrapporre chip di natura diversa come chip di calcolo sovrapposti a chip di ram, ottimizzando di fatto al massimo lo spazio e la velocità di trasferimento dei dati, e favorendo così la produzione di veri e propri sistemi SOP (System on Package), senza la necessità di dover usare pcb di grandi dimensioni.

IBM quindi si dimostra sempre più leader nella ricerca tecnologica, persino in quella del raffreddamento a liquido, anche se riducendone le dimensioni a livello microscopico, e consentendo di fatto in un prossimo futuro di aumentare in via esponenziale la potenza di calcolo dei chip ad ogni nuova generazione, a seconda del numero di strati di chip sovrapposti. Con buona pace della legge di Moore.

[Images courtesy of IBM]